## **OPAMPS**

N.Raju Associate Professor ECE

Jyothishmathi Institute of Technology & Science

#### **Sequential Circuits**

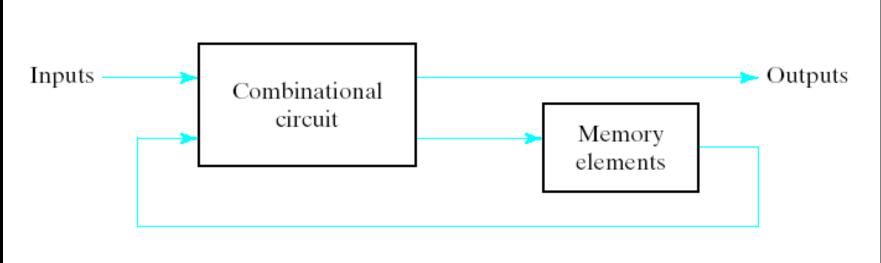

Every digital system is likely to have combinational circuits, most systems encountered in practice also include storage elements, which require that the system be described in term of sequential logic.

Fig. 5-1 Block Diagram of Sequential Circuit

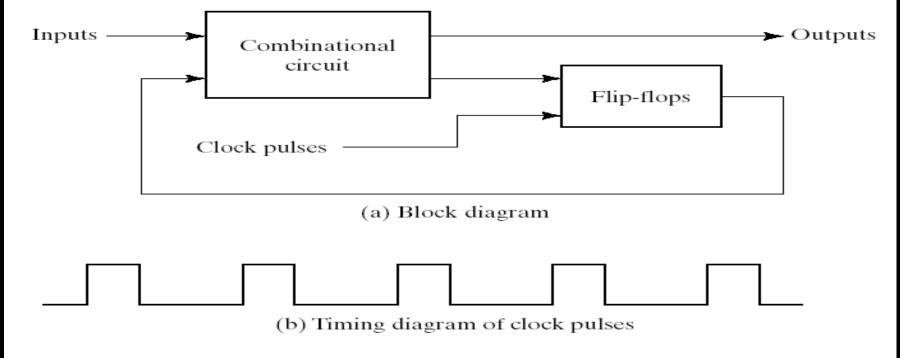

# Synchronous Clocked Sequential Circuit

A sequential circuit may use many flip-flops to store as many bits as necessary. The outputs can come either from the combinational circuit or from the flip-flops or both.

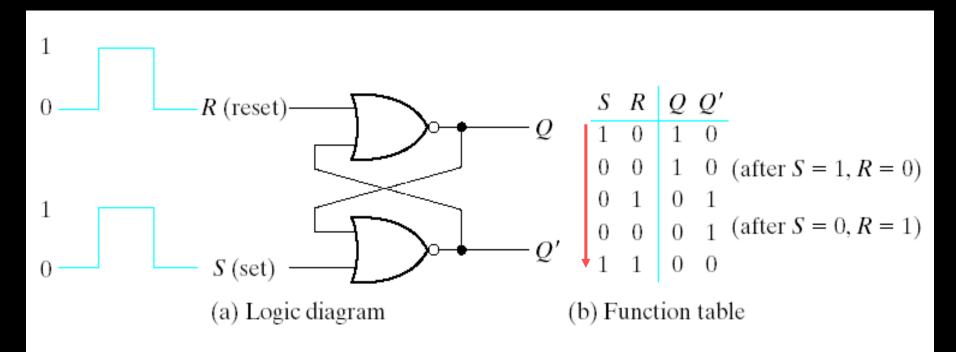

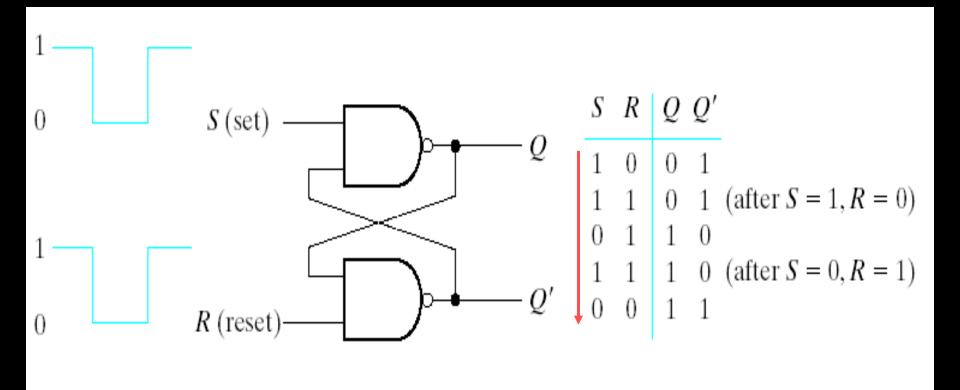

#### Latches SR Latch

The SR latch is a circuit with two cross-coupled NOR gates or two cross-coupled NAND gates. It has two inputs labeled S for set and R for reset.

Fig. 5-3 SR Latch with NOR Gates

#### **SR Latch with NAND Gates**

(a) Logic diagram

Fig. 5-4 SR Latch with NAND Gates

(b) Function table

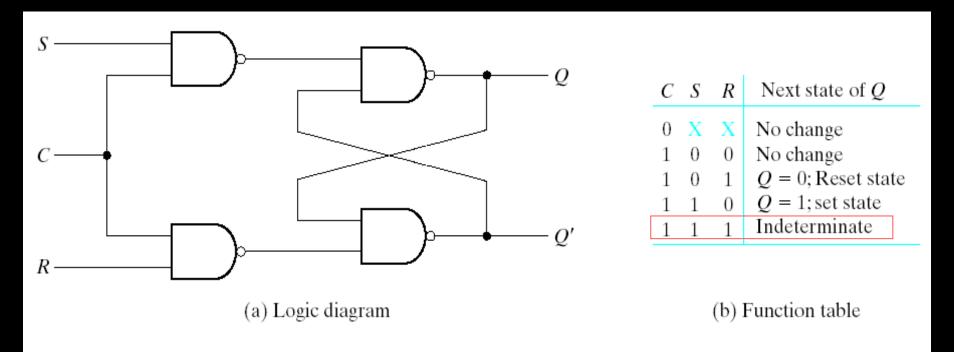

## **SR Latch with Control Input**

The operation of the basic SR latch can be modified by providing an additional control input that determines when the state of the latch can be changed. In Fig. 5-5, it consists of the basic SR latch and two additional NAND gates.

Fig. 5-5 SR Latch with Control Input

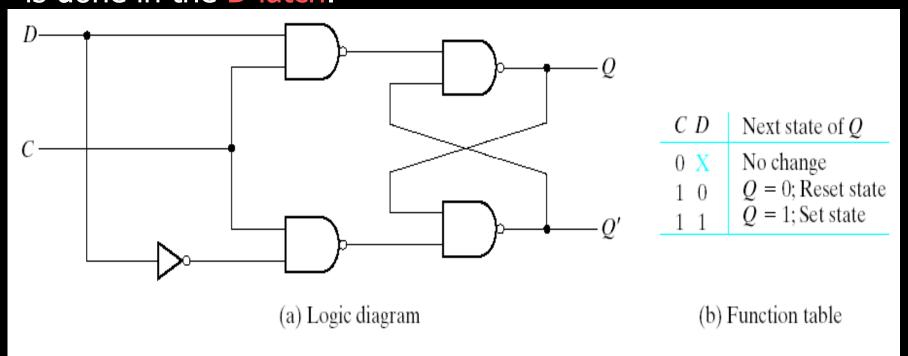

#### **D** Latch

One way to eliminate the undesirable condition of the indeterminate state in SR latch is to ensure that inputs S and R are never equal to 1 at the same time in Fig 5-5. This is done in the D latch.

Fig. 5-6 D Latch

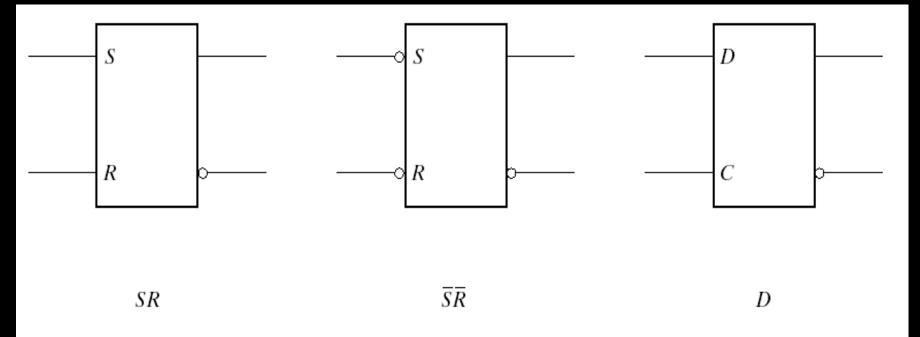

## **Graphic Symbols for latches**

A latch is designated by a rectangular block with inputs on the left and outputs on the right. One output designates the normal output, and the other designates the complement output.

Fig. 5-7 Graphic Symbols for Latches

#### Flip-Flops

The state of a latch or flip-flop is switched by a change in the control input. This momentary change is called a trigger and the transition it cause is said to trigger the flip-flop. The D latch with pulses in its control input is essentially a flip-flop that is triggered every time the pulse goes to the logic 1 level. As long as the pulse input remains in the level, any changes in the data input will change the output and the state of the latch.

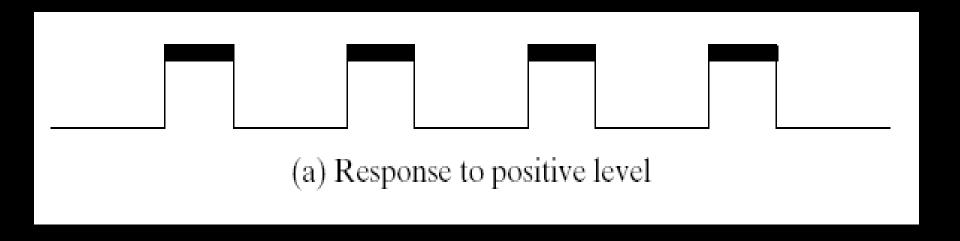

## **Clock Response in Latch**

In Fig (a) a positive level response in the control input allows changes, in the output when the D input changes while the clock pulse stays at logic 1.

## **Clock Response in Flip-Flop**

## Edge-Triggered D Flip-Flop

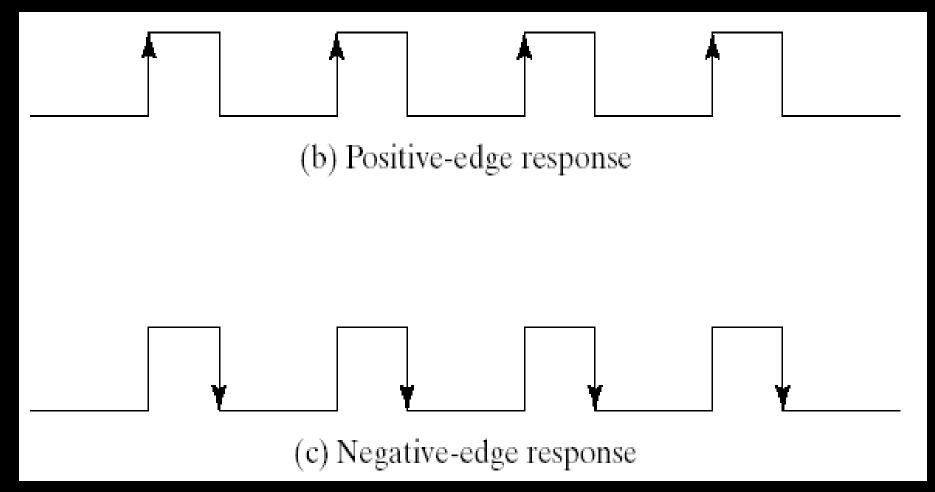

The first latch is called the master and the second the slave. The circuit samples the D input and changes its output Q only at the negative-edge of the controlling clock.

#### D-Type Positive-Edge-Triggered Flip-Flop

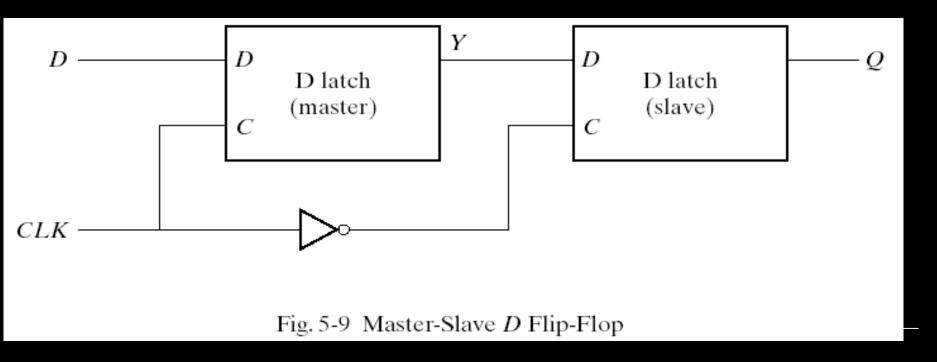

Another more efficient construction of an edge-triggered D flip-flop uses three SR latches. Two latches respond to the external D(data) and CLK(clock) inputs. The third latch provides the outputs for the flip-flop.

Fig. 5-10 D-Type Positive-Edge-Triggered Flip-Flop

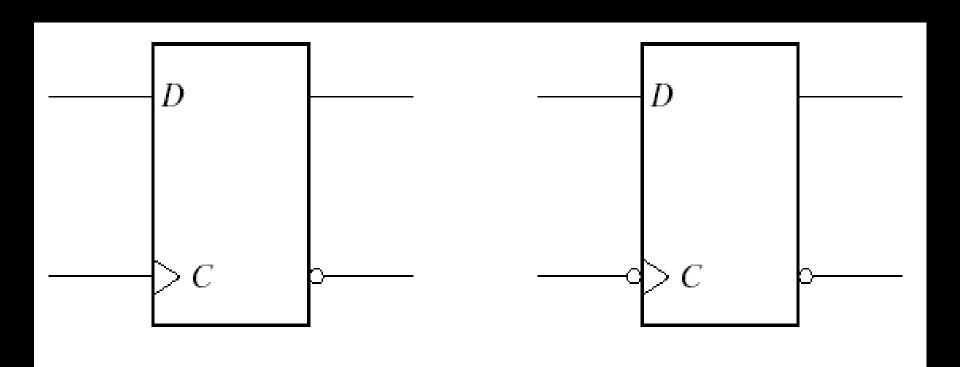

#### **Graphic Symbol for Edge-Triggered D Flip-Flop**

(a) Positive-edge

(a) Negative-edge

Fig. 5-11 Graphic Symbol for Edge-Triggered D Flip-Flop

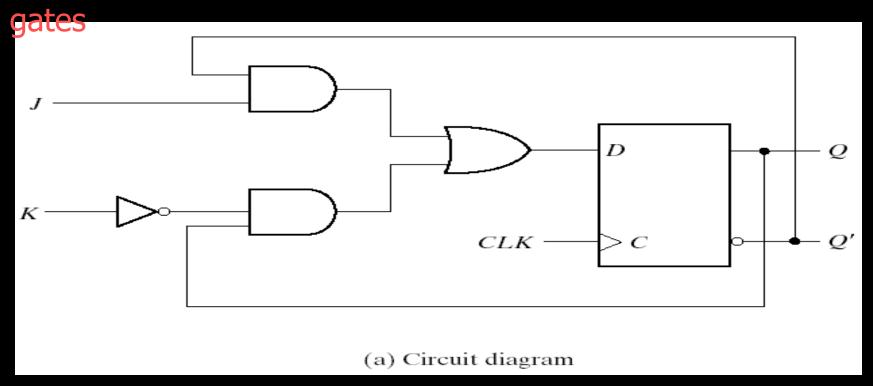

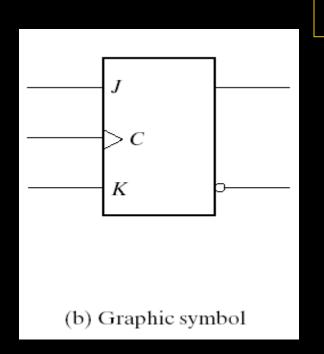

## Other Flip-Flops JK Flip-Flop

There are three operations that can be performed with a flip-flop: set it to 1, reset it to 0, or complement its output. The JK flip-flop performs all three operations. The circuit diagram of a JK flip-flop constructed with a D flip-flop and

## JK Flip-Flop

The J input sets the flip-flop to 1, the K input resets it to 0, and when both inputs are enabled, the output is complemented. This can be verified by investigating the circuit applied to the D input:

$$D = J Q' + K' Q$$

| JK Flip-Flop |   |             |              |

|--------------|---|-------------|--------------|

| J            | K | Q(t+1)      | cions me inp |

| 0            | 0 | Q(t)        | No change    |

| 0            | 1 | 0           | Reset        |

| 1            | 0 | I to one ad | Set          |

| 1            | 1 | Q'(t)       | Complement   |

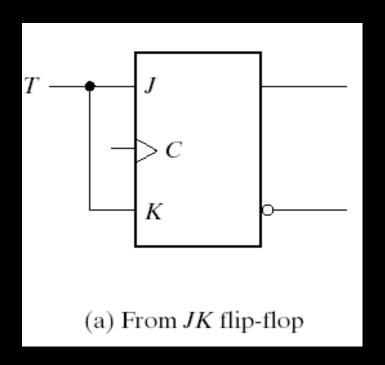

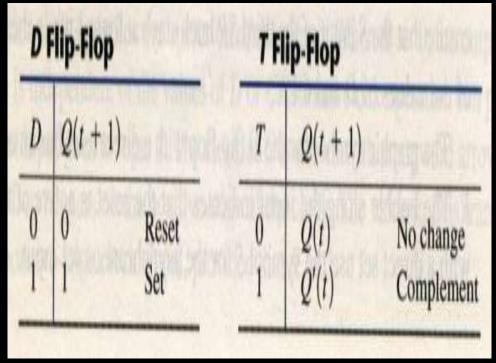

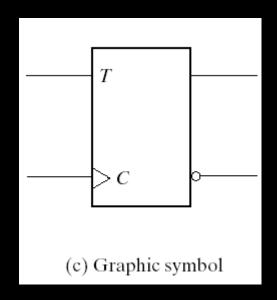

## T Flip-Flop

The T(toggle) flip-flop is a complementing flip-flop and can be obtained from a JK flip-flop when inputs J and K are tied together.

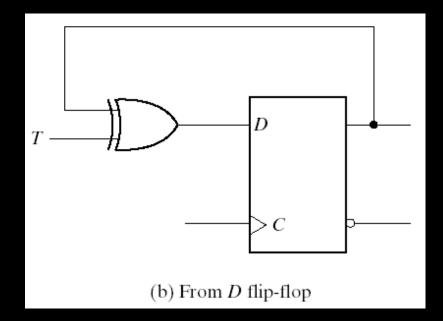

## T Flip-Flop

The T flip-flop can be constructed with a D flip-flop and an exclusive-OR gates as shown in Fig. (b). The expression for the D input is

$$D = T \bigoplus Q = TQ^{+} + T^{+}Q$$

## **Characteristic Equations**

D flip-flop Characteristic Equations

$$Q(t+1) = D$$

JK flip-flop Characteristic Equations

$$Q(t + 1) = JQ' + K'Q$$

T flip-flop Characteristic Equations

$$Q(t + 1) = T \oplus Q = TQ^+ + T^Q$$

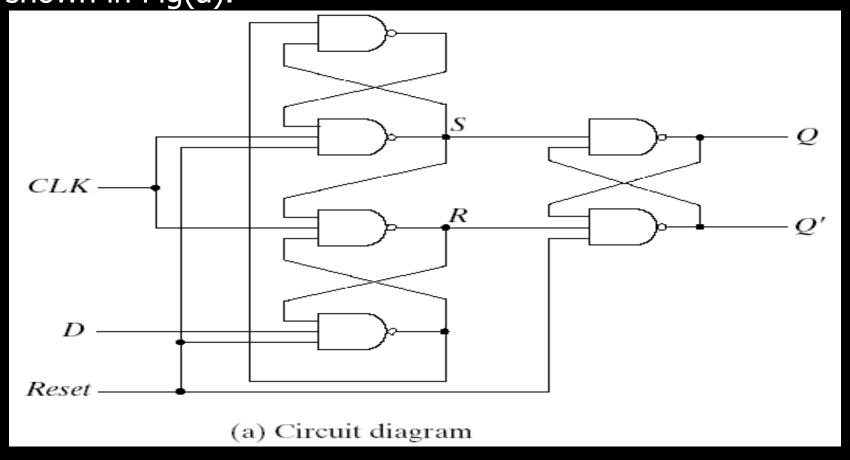

## **Direct Inputs**

Some flip-flops have asynchronous inputs that are used to force the flip-flop to a particular state independent of the clock. The input that sets the flip-flop to 1 is called present or direct set. The input that clears the flip-flop to 0 is called clear or direct reset. When power is turned on a digital system, the state of the flip-flops is unknown. The direct inputs are useful for bringing all flip-flops in the system to a known starting state prior to the clocked operation.

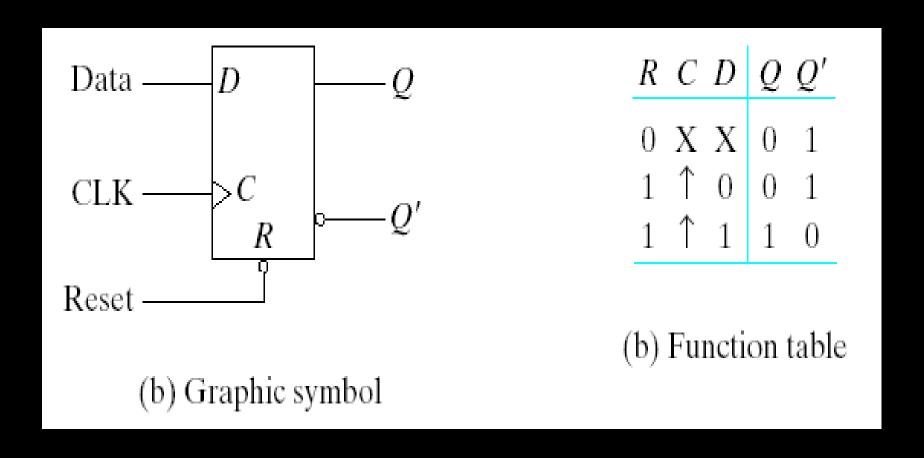

## D Flip-Flop with Asynchronous Reset

A positive-edge-triggered D flip-flop with asynchronous reset is shown in Fig(a).

## **D Flip-Flop with Asynchronous Reset**